Giới thiệu

Truy cập bộ nhớ và tính toán là hai chức năng chính trong bất kỳ hệ thống máy tính nào. Trong những thập kỷ qua, khả năng tính toán của bộ xử lý đã được hưởng lợi rất nhiều từ Định luật Moore, định luật này hầu như hàng năm đều đưa các bóng bán dẫn nhỏ hơn và nhanh hơn vào khuôn silicon. Mặt khác, bộ nhớ hệ thống đang thoái lui. Xu hướng thu hẹp công nghệ chế tạo cho một hệ thống đang khiến việc truy cập bộ nhớ chậm hơn rất nhiều. Sự mất cân bằng này khiến hiệu năng của hệ thống máy tính bị hạn chế do khả năng truy cập bộ nhớ; điều này được gọi là vấn đề “bức tường bộ nhớ”. Vấn đề trở nên tồi tệ hơn đối với các ứng dụng mô hình ngôn ngữ lớn (LLM) vì chúng yêu cầu nhiều bộ nhớ và khả năng tính toán hơn. Do đó, cần có nhiều quyền truy cập bộ nhớ hơn để có thể thực thi các mô hình lớn hơn đó.

Trong blog này, chúng tôi sẽ điều tra tác động của tắc nghẽn truy cập bộ nhớ đến kết quả suy luận LLM. Đối với các thử nghiệm, chúng tôi đã chọn mô hình trò chuyện Llama2 chạy trên máy chủ Dell PowerEdge HS5610 với Bộ xử lý có khả năng mở rộng Intel ® Xeon ® thế hệ thứ 4 . Để phân tích định lượng, chúng tôi sẽ sử dụng công cụ hồ sơ Intel – Intel® VTune™ Profiler để nắm bắt thông tin truy cập bộ nhớ trong khi chạy khối lượng công việc. Sau khi xác định vị trí của các tắc nghẽn truy cập bộ nhớ, chúng tôi đề xuất các kỹ thuật và cấu hình khả thi để giảm thiểu sự cố trong phiên kết luận.

Lý lịch

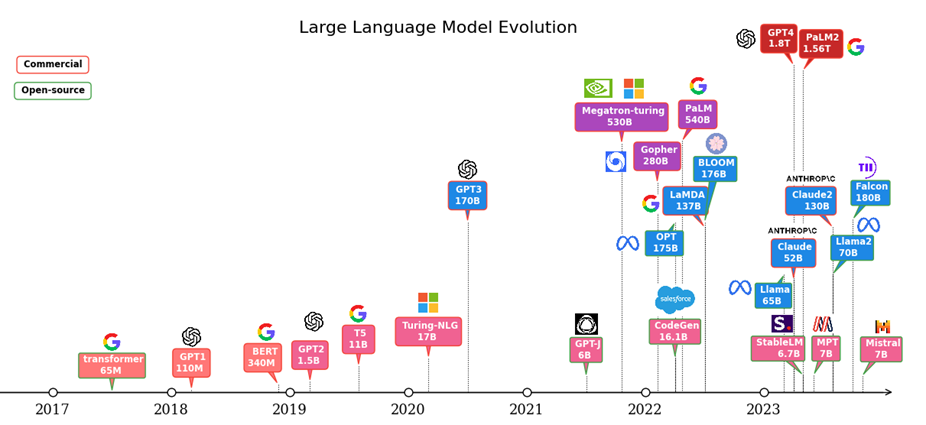

Xử lý ngôn ngữ tự nhiên (NLP) đã được hưởng lợi rất nhiều từ kiến trúc máy biến áp kể từ khi nó được giới thiệu vào năm 2017 [1]. Quỹ đạo của các mô hình NLP đã được chuyển sang các kiến trúc dựa trên máy biến áp nhờ các tính năng song song hóa và khả năng mở rộng của nó so với các kiến trúc Mạng thần kinh tái phát (RNN) truyền thống. Nghiên cứu cho thấy quy luật mở rộng của các mô hình ngôn ngữ dựa trên máy biến áp, trong đó độ chính xác liên quan chặt chẽ đến kích thước mô hình, kích thước tập dữ liệu và lượng tính toán [2]. Điều này đã truyền cảm hứng cho sự quan tâm đến việc sử dụng Mô hình ngôn ngữ lớn (LLM) để có được các tác vụ phức tạp và có độ chính xác cao. Hình 1 cho thấy sự phát triển của LLM kể từ khi kiến trúc máy biến áp được phát minh. Chúng ta có thể thấy các thông số của LLM đã tăng lên đáng kể trong 5 năm qua. Xu hướng này đang tiếp tục. Như trong hình, hầu hết các LLM ngày nay đều có hơn 7 tỷ tham số. Một số model như GPT4 và PaLM2 có thông số nghìn tỷ để hỗ trợ các tính năng đa chế độ.

Hình 1: Sự phát triển của LLM

Điều đi kèm với các mô hình lớn là những thách thức đối với hệ thống phần cứng trong việc đào tạo và suy luận các mô hình đó. Một mặt, tính toán cần thiết là rất lớn vì nó tỷ lệ thuận với kích thước mô hình. Mặt khác, việc truy cập bộ nhớ rất tốn kém. Điều này chủ yếu xuất phát từ giao tiếp ngoài chip và kiến trúc bộ đệm phức tạp cần thiết để hỗ trợ các tham số và tính toán mô hình lớn.

Thiết lập thử nghiệm

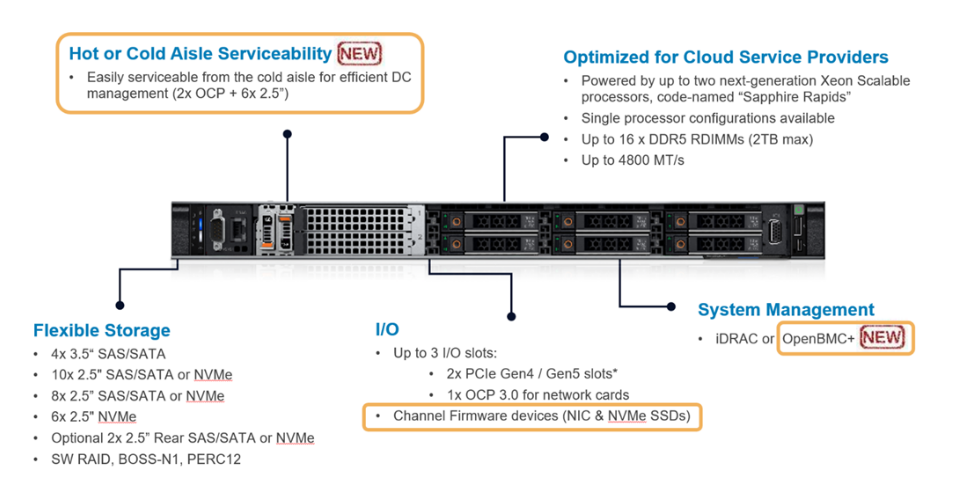

Nền tảng phần cứng mà chúng tôi sử dụng cho nghiên cứu này là HS5610, đây là máy chủ 16G được tối ưu hóa cho đám mây mới nhất trong danh mục sản phẩm của Dell. Hình 2 đưa ra cái nhìn tổng quan về HS5610. Nó được thiết kế với các tính năng CSP mang lại lợi ích tương tự với các tính năng & quản lý PowerEdge đầy đủ như máy chủ Dell chính thống, cũng như quản lý mở (OpenBMC), dịch vụ lối đi lạnh, chương trình cơ sở kênh và các dịch vụ. Máy chủ có hai ổ cắm với CPU Intel ® Xeon ® 32 nhân thế hệ thứ 4 của Intel trên mỗi ổ cắm. Công suất TDP cho mỗi CPU là 250W. Bảng 1 và Bảng 2 hiển thị chi tiết về cấu hình máy chủ và thông số kỹ thuật CPU.

Hình 2: PowerEdge HS5610 [3]

| Bộ sưu tập sản phẩm | Bộ xử lý có khả năng mở rộng Intel ® Xeon ® thế hệ thứ 4 |

| Tên bộ xử lý | Bạch kim 8480+ |

| Trạng thái | Đã ra mắt |

| Số lõi CPU | 32 |

| số chủ đề | 64 |

| Tần số cơ sở | 2,0 GHz |

| Tốc độ Turbo tối đa | 3,8 GHz |

| Bộ đệm L3 | 64 MB |

| Loại bộ nhớ | DDR5 4800 tấn/giây |

| Hỗ trợ bộ nhớ ECC | Đúng |

Bảng 1: Cấu hình máy chủ HS5610

| Tên hệ thống | PowerEdge HS5610 |

| Trạng thái | Có sẵn |

| Loại hệ thống | Trung tâm dữ liệu |

| Số nút | 1 |

| Mô hình bộ xử lý máy chủ | Bộ xử lý có khả năng mở rộng Intel ® Xeon ® thế hệ thứ 4 |

| Bộ xử lý máy chủ trên mỗi nút | 2 |

| Số lượng lõi của bộ xử lý máy chủ | 32 |

| Tần số bộ xử lý máy chủ | Tăng tốc Turbo 2,0 GHz, 3,8 GHz |

| Dung lượng bộ nhớ máy chủ | DIMM 1TB, 16 x 64GB 4800 MHz |

| Dung lượng lưu trữ máy chủ | 4,8 TB, NVME |

Bảng 2: Thông số kỹ thuật của bộ xử lý có khả năng mở rộng Intel ® Xeon ® 32 nhân thế hệ thứ 4

Ngăn xếp phần mềm và cấu hình hệ thống

Cấu hình hệ thống và ngăn xếp phần mềm được sử dụng cho lần gửi này được tóm tắt trong Bảng 3. Các tối ưu hóa đã được thực hiện đối với khung PyTorch và thư viện Transformers để giải phóng khả năng hướng dẫn AI của CPU Xeon. Ngoài ra, một công cụ cấp thấp – Intel ® Neural Compressor đã được sử dụng để lượng tử hóa với độ chính xác cao.

| hệ điều hành | CentOS Stream 8 (GNU/Linux x86_64) |

| SW suy luận tối ưu hóa Intel® | OneDNN™ Deep Learning, ONNX, Intel ® Extension cho PyTorch (IPEX), Intel ® Extension cho Transformers (ITREX), Intel ® Neural Compressor |

| Chế độ bộ nhớ ECC | TRÊN |

| Cấu hình bộ nhớ máy chủ | 1TiB |

| Chế độ tăng tốc | TRÊN |

| Bộ điều chỉnh tần số CPU | Hiệu suất |

Bảng 3: Ngăn xếp phần mềm và cấu hình hệ thống

Mô hình được thử nghiệm là mô hình Llama2-chat-hf với 13 tỷ tham số (Llama2-13b-chat-hf). Mô hình này dựa trên mô hình 13 tỷ Llama2 được đào tạo trước và được tinh chỉnh bằng phản hồi của con người cho các ứng dụng chatbot. Mẫu Llama2 có các phiên bản kích thước nhẹ (7b), trung bình (13b) và nặng (70b).

Công cụ hồ sơ được sử dụng trong thử nghiệm là Intel® VTune™. Nó là một công cụ phân tích hiệu suất cấp thấp mạnh mẽ dành cho CPU x86 hỗ trợ các thuật toán, kiến trúc vi mô, tính song song và phân tích liên quan đến IO, v.v. Đối với các thử nghiệm, chúng tôi sử dụng phân tích truy cập bộ nhớ trong danh mục kiến trúc vi mô. Lưu ý Intel® VTune™ tiêu tốn tài nguyên phần cứng đáng kể, điều này sẽ ảnh hưởng đến kết quả hiệu năng nếu chúng tôi chạy công cụ cùng với khối lượng công việc. Vì vậy, chúng tôi sử dụng nó làm công cụ hồ sơ/gỡ lỗi để điều tra nút thắt cổ chai. Các con số hiệu suất mà chúng tôi chứng minh ở đây đang chạy mà không bật Intel® VTune™.

Các thí nghiệm được nhắm mục tiêu để bao gồm những điều sau đây:

- Hiệu suất ổ cắm đơn so với hiệu suất ổ cắm kép để chứng minh tác động truy cập bộ nhớ NUMA.

- Hiệu suất theo các số lõi CPU khác nhau trong một ổ cắm duy nhất để chứng minh tác động truy cập bộ nhớ cục bộ.

- Hiệu suất với lượng tử hóa khác nhau để chứng minh tác động lượng tử hóa.

- Kết quả truy cập bộ nhớ Intel® VTune™.

Vì Intel® VTune™ có yêu cầu về thời lượng ghi tối thiểu và kích thước ghi tối đa nên chúng tôi tập trung vào việc ghi lại kết quả cho kiểu máy có kích thước trung bình (Llama2-13b-chat-hf). Điều này ngăn cản thời gian suy luận ngắn/dài, do đó tránh được vấn đề thiếu tải hoặc quá tải. Tất cả các thử nghiệm đều dựa trên kích thước lô bằng 1. Hiệu suất được đặc trưng bởi độ trễ hoặc thông lượng. Để giảm sai số đo, phép suy luận được thực hiện 10 lần để lấy giá trị trung bình. Quá trình khởi động bằng cách tải tham số và chạy thử nghiệm mẫu được thực hiện trước khi chạy suy luận đã xác định.

Kết quả

Đối với phần này, chúng tôi trình bày kết quả hiệu suất về mặt thông lượng cho các kịch bản ổ cắm đơn và ổ cắm kép theo các loại lượng tử hóa khác nhau, sau đó là kết quả thu thập Intel ® VTune™.

Kết quả một ổ cắm theo các loại lượng tử hóa khác nhau:

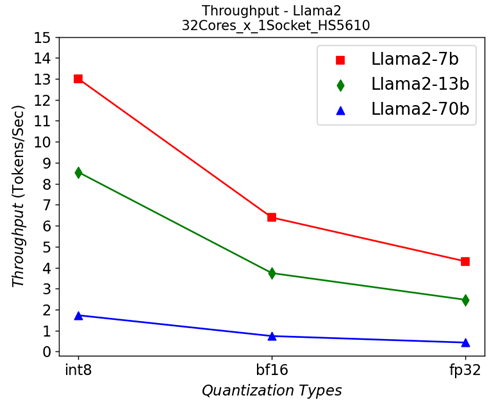

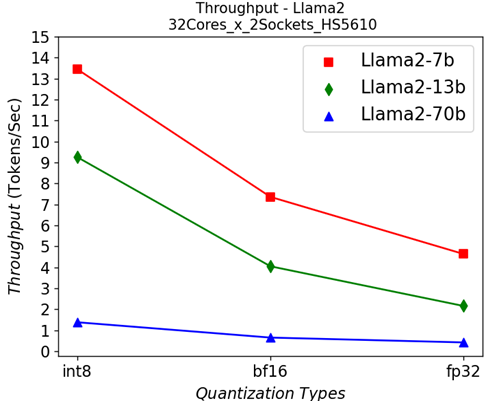

Hình 3: Thông lượng một socket trong máy chủ HS5610 chạy mô hình Llama2 theo các kiểu lượng tử hóa khác nhau

Hình 3 cho thấy thông lượng khi chạy các mô hình trò chuyện Llama2 khác nhau với các kiểu lượng tử hóa khác nhau trên một ổ cắm. Lệnh “numactl” được sử dụng để giới hạn khối lượng công việc trong một CPU 32 lõi. Từ kết quả, chúng ta có thể thấy rằng lượng tử hóa giúp cải thiện hiệu suất trên các mô hình khác nhau rất nhiều.

|

|

|

(Một) |

(b) |

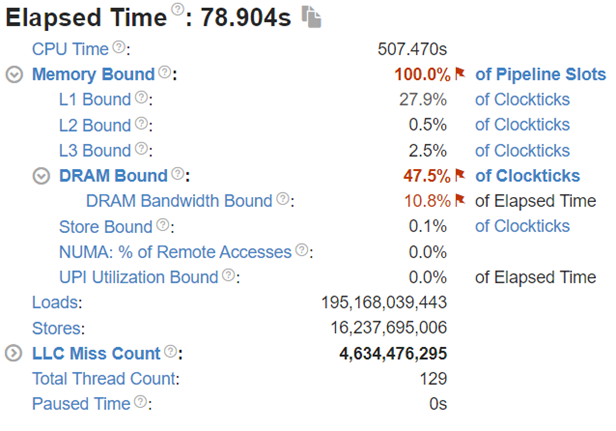

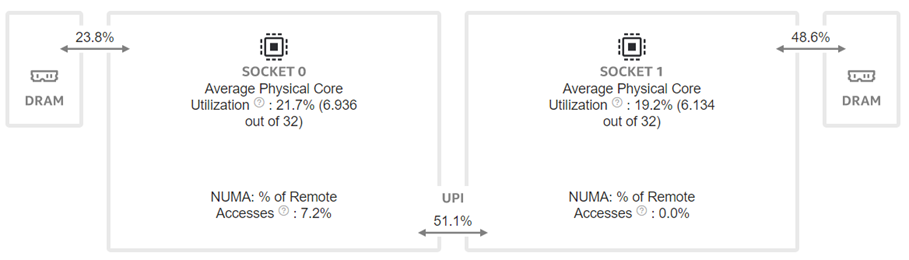

Hình 4: Kết quả phân tích bộ nhớ Intel® VTune™ cho kết quả fp32 socket đơn :

(Một). sơ đồ băng thông và sử dụng (b). phân tích thời gian trôi qua

|

|

|

(Một) |

(b) |

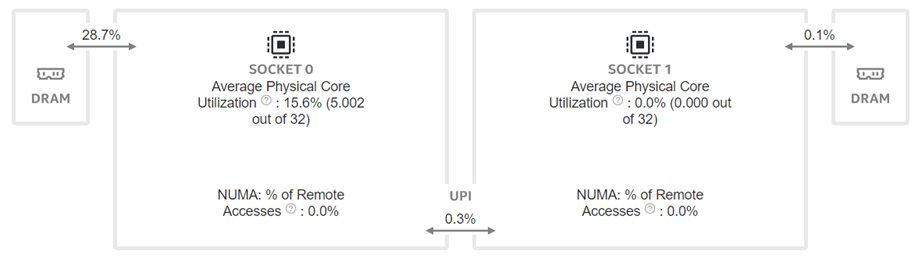

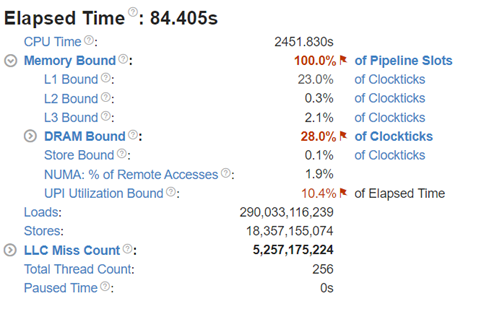

Hình 5: Kết quả phân tích bộ nhớ Intel® VTune™ cho kết quả bf16 socket đơn :

(Một). sơ đồ băng thông và sử dụng (b). phân tích thời gian trôi qua

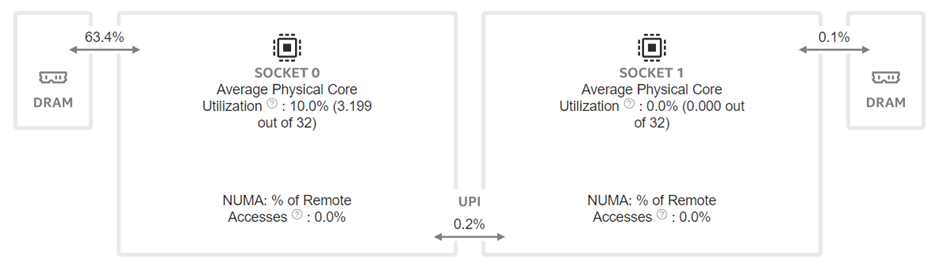

Để hiểu rõ hơn điều gì sẽ xảy ra ở cấp độ thấp hơn, chúng ta sẽ lấy mô hình 13 tỷ Llama2 làm ví dụ. Chúng tôi sẽ sử dụng Intel® VTune™ để ghi lại sơ đồ sử dụng và băng thông cũng như phân tích thời gian đã trôi qua cho loại dữ liệu fp32 (được hiển thị trong Hình 4) và sử dụng loại dữ liệu bf16 (được hiển thị trong Hình 5). Chúng ta có thể thấy rằng bằng cách giảm các bit đại diện, băng thông cần thiết cho giao tiếp CPU và DRAM sẽ giảm. Trong trường hợp này, mức sử dụng DRAM giảm từ 63,4% đối với fp32 (được hiển thị trong Hình 4 (a)) xuống 28,7% (được hiển thị trong Hình 4 (b)). Điều này cũng chỉ ra rằng dữ liệu trọng lượng có thể đến chip CPU nhanh hơn. Bây giờ chúng ta có thể hưởng lợi từ việc giao tiếp bộ nhớ nhanh hơn. mức sử dụng CPU cũng tăng từ 10% (thể hiện trong Hình 4 (a)) đối với fp32 lên 15,6% đối với bf16 (thể hiện trong Hình 4 (b)). Cả truy cập bộ nhớ nhanh hơn và sử dụng CPU tốt hơn đều dẫn đến hiệu suất tốt hơn với mức tăng thông lượng hơn 50% (từ 2,47 mã thông báo/giây cho fp32 lên 3,74 mã thông báo/giây) như trong Hình 3. Tìm hiểu sâu hơn với phân tích thời gian đã trôi qua được hiển thị trong Hình Như được hiển thị trong Hình 4 (b) và Hình 5 (b), bộ đệm L1 là một trong những vị trí tắc nghẽn hiệu năng trên chip. Lượng tử hóa làm giảm khả năng nhiệm vụ bị đình trệ.

Kết quả ổ cắm kép theo các loại lượng tử hóa khác nhau:

Hình 6: Thông lượng socket kép trong máy chủ HS5610 chạy mô hình Llama2 theo các kiểu lượng tử hóa khác nhau

|

|

|

(Một) |

(b) |

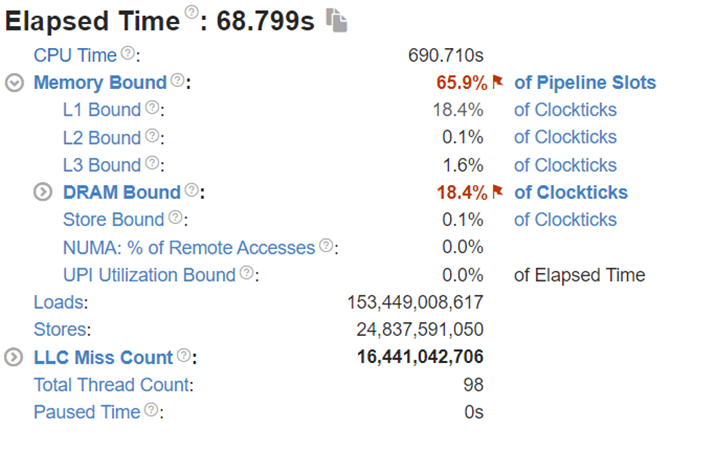

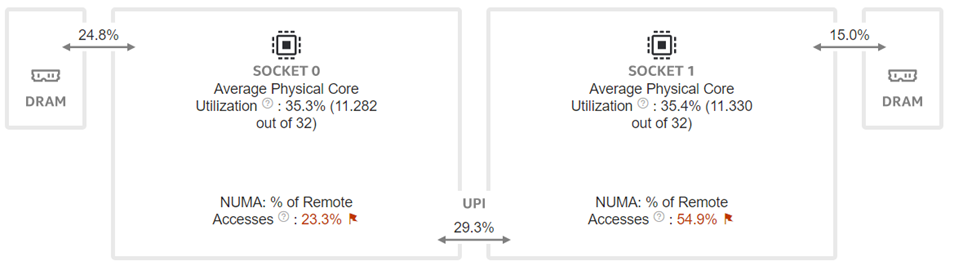

Hình 7: Kết quả phân tích bộ nhớ Intel® VTune™ cho kết quả fp32 socket kép :

(Một). sơ đồ băng thông và sử dụng (b). phân tích thời gian trôi qua

|

|

|

(Một) |

(b) |

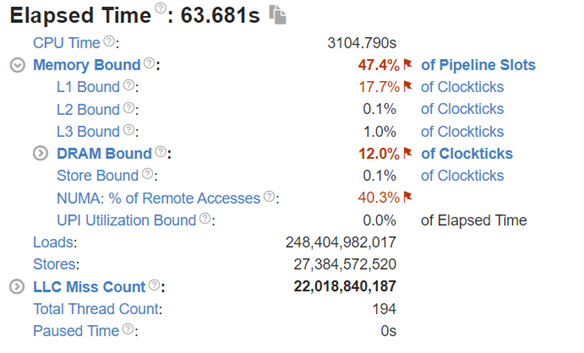

Hình 8: Kết quả phân tích bộ nhớ Intel® VTune™ cho kết quả bf16 socket kép :

(Một). sơ đồ băng thông và sử dụng (b). phân tích thời gian trôi qua

Bây giờ chuyển sang các kịch bản ổ cắm kép được hiển thị trong Hình 6-8, chúng tôi có những quan sát tương tự về tác động của lượng tử hóa: Lượng tử hóa làm tăng mức sử dụng CPU và giảm tắc nghẽn bộ đệm L1, do đó tăng thông lượng trên các mô hình Llama2 khác nhau.

So sánh hiệu suất giữa các kịch bản ổ cắm đơn (được hiển thị trong Hình 3) và ổ cắm kép (được hiển thị trong Hình 6) cho thấy sự cải thiện hiệu suất không đáng kể. Như đã thấy trong Hình 7 và 8, mặc dù chúng tôi sử dụng CPU tốt hơn nhưng giao tiếp giữa hai ổ cắm (truy cập bộ nhớ UPI hoặc NUMA) lại trở thành nút thắt cổ chai chính làm mất đi lợi ích của việc có nhiều lõi điện toán hơn.

Phần kết luận

Dựa trên kết quả thử nghiệm cho các mô hình Llama2 khác nhau với các cấu hình khác nhau, chúng tôi có kết luận như sau:

- Lượng tử hóa cải thiện hiệu suất trên các mô hình có trọng số khác nhau bằng cách giảm tắc nghẽn bộ đệm L1 và tăng mức sử dụng CPU. Nó cũng chỉ ra rằng chúng ta có thể tối ưu hóa TCO bằng cách giảm yêu cầu bộ nhớ (về dung lượng và tốc độ) nếu chúng ta có thể lượng tử hóa mô hình một cách chính xác.

- Giao tiếp qua socket từ quyền truy cập bộ nhớ UPI hoặc NUMA là một nút thắt cổ chai đáng kể có thể ảnh hưởng đến hiệu suất. Tối ưu hóa bao gồm việc giảm giao tiếp giữa các ổ cắm. Ví dụ, việc phân vùng mô hình tốt hơn là rất quan trọng. Ngoài ra, điều này cũng chỉ ra rằng việc thực thi một khối lượng công việc trên một CPU chuyên dụng duy nhất có đủ số lõi là điều cần thiết để cân nhắc về chi phí và hiệu suất.

Bài viết mới cập nhật

Dell Storage Engines: Tăng tốc suy luận AI với PowerScale và ObjectScale

Giải pháp chuyển tải bộ nhớ đệm KV của Dell cho ...

Bảo vệ Nhà máy AI

Áp dụng phương pháp tiếp cận kiến trúc để bảo mật ...

Tiến lên mạnh mẽ với Dell PowerMax: Vượt mặt Hitachi VSP 5000

Dell PowerMax mang lại khả năng phục hồi, hiệu suất và ...

Đẩy nhanh đổi mới AI: Sức mạnh của quyền truy cập mở

Từ các mô hình tiên tiến đến các ứng dụng cấp ...